Physical design course level1

Course overview :

1. 15+ week program

2. Program covers all aspects of Netlist2GDS flow

3. Every topic and sub-topics are discussed in detail with practical aspects and hands-on sessions

4. Covers advanced concepts in Digital Design, CMOS, PnR flow, Signoff STA, Physical Verification, Low Power methodologies, Logic Equivalence Check and TCL scripting

5. Our designs are co-developed with inputs from industry experts

6. Soft Skill training

7. Resume preparation support

8. Regular assessment test to identify the areas that candidate needs to improve

9. Enable learning through regular theory and lab assignments

10. Course completion Certificate after successful completion of the program

11. The path to industry would be very clear once this program is successfully completed

12. Labs can be accessed through VPN (24×7) from anywhere

Syllabus:

Module 1 Advanced Digital Design

Module 2 Introduction of CMOS Circuits

Module 2 Introduction to Physical Design Flow & Inputs

Module 3 Design Planning (Floor-plan)

Module 4 Power-Routing

Module 5 Static Timing Analysis

Module 6 Pre-Placement & Std-Cell Placement

Module 7 Timing Optimization

Module 8 CTS & Post-CTS Timing Optimization

Module 9 Routing

Module 10 Sign-off Checks

Module 11 Timing Closure & ECO Implementation

Module 12 Low-Power Implementation

Module 13 Introduction to Advanced STA Topics

Module 14 TCL Scripting

Module 15 Final Projects (Multiple)

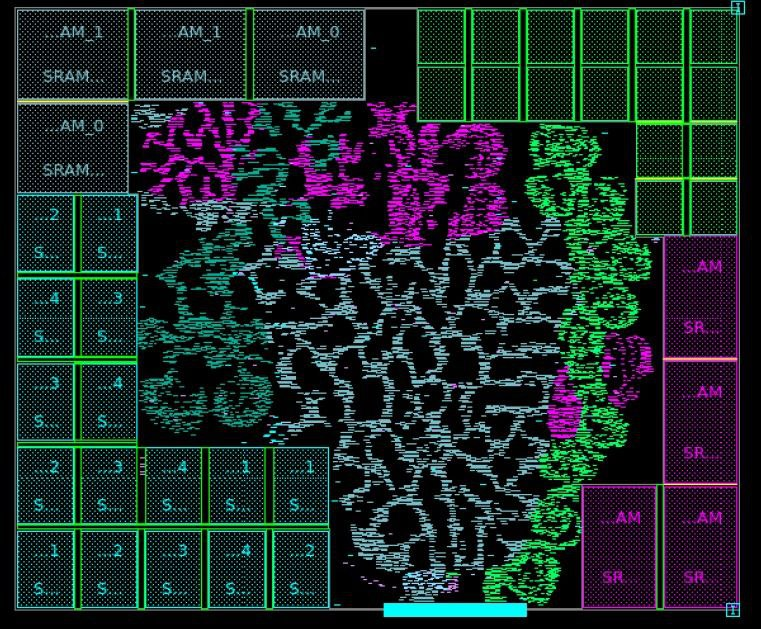

Lab - Tools and project design

Lab:

Complex block level implementation

Designs covering full PnR end to end.

Tools and Project Design:

Most prominent and widely used tools in the industry

Who can Attend

Engineering Graduates (B.Tech, B.E., BS)

Engineering Post-Graduates (M.Tech, M.E., M.S.)

Experienced Engineers who want to change their domain to Physical Design

Experienced Engineers who want to improve their Physical Design skills

College faculties who want to gain Industry knowledge

our Trainers details

Trainer 1

Semiconductor industry veteran with about 20 years and expert in the areas of RTL Coding, Physical Design and STA

Immense knowledge in algorithmic level of implementation tools like Synopsys, Cadence etc

Have held multiple positions like Product Engineering, Design and Application Engineering and driven start-ups’

Experienced in block level, sub-system level and Full Chip level Synthesis, PD and STA closures

Have worked for companies like Cadence, Magma, Synopsys, Infineon, Mediatek, Qualcomm, Intel across geographies

500+ Engineers have been trained across the globe

Trainer 2

Comes with immense experience in the spectrum of Physical Design having done more than 25 tapeouts

Executed Full Chip, Sub-System and block levels creating partitions

Have worked on Signoff like STA, PV, IR etc.

Experienced with 6 years in training who has held various levels of trainings

Trained about 650+ engineers

Trainer brings in experience from multiple MNCs with about 16+ years of industry experience

Trainer is leading a team of 60+ engineers currently

Working on Full Chip and methodology development

Technology node expertise from 7nm till 250nm across various foundries

Strong hands on experience in Synopsys and Cadence tool sets

Strong in TCL and PERL